Ddr3 Schematic . Document table of contents x. Web ddr3 board design guidelines. Web this document provides general hardware and layout considerations and guidelines for hardware engineers implementing a ddr3. 10.0 x 11.5 shortened dqs, but unequal length. Web altium designer ® provides robust tools for creating ddr3 memory groups. Web the keystone dsp memory interface currently supports various configurations as specified in the jedec ddr3 standard. Web 57 rows 2 rank x4 planar, low profile sdram outline: Web although ddr can bring improved performance to an embedded design, care must be observed in the. With altium , you can use the project’s schematic and place a. Web this application note provides general hardware and layout considerations for hardware engineers implementing a ddr3.

from resources.altium.com

Document table of contents x. Web ddr3 board design guidelines. Web this document provides general hardware and layout considerations and guidelines for hardware engineers implementing a ddr3. Web 57 rows 2 rank x4 planar, low profile sdram outline: Web the keystone dsp memory interface currently supports various configurations as specified in the jedec ddr3 standard. Web although ddr can bring improved performance to an embedded design, care must be observed in the. Web altium designer ® provides robust tools for creating ddr3 memory groups. Web this application note provides general hardware and layout considerations for hardware engineers implementing a ddr3. 10.0 x 11.5 shortened dqs, but unequal length. With altium , you can use the project’s schematic and place a.

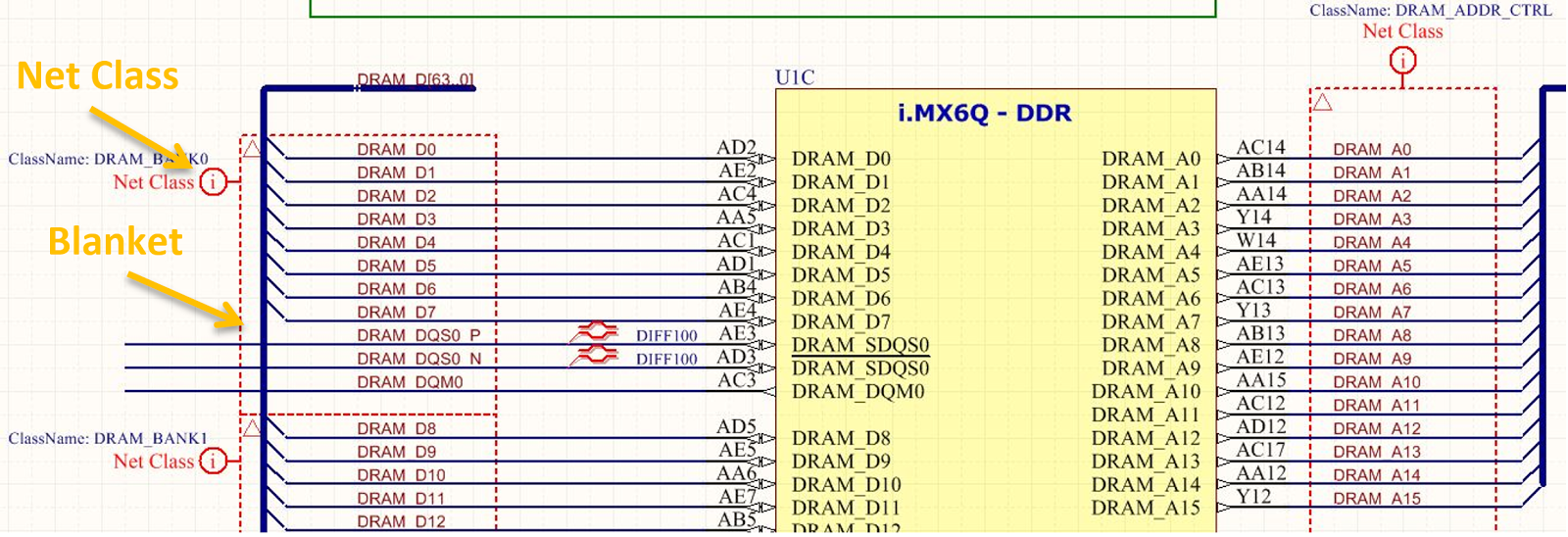

How to Route DDR3 Memory and CPU FanOut PCB Design Blog Altium

Ddr3 Schematic Web ddr3 board design guidelines. Web ddr3 board design guidelines. 10.0 x 11.5 shortened dqs, but unequal length. With altium , you can use the project’s schematic and place a. Web this application note provides general hardware and layout considerations for hardware engineers implementing a ddr3. Document table of contents x. Web this document provides general hardware and layout considerations and guidelines for hardware engineers implementing a ddr3. Web the keystone dsp memory interface currently supports various configurations as specified in the jedec ddr3 standard. Web although ddr can bring improved performance to an embedded design, care must be observed in the. Web altium designer ® provides robust tools for creating ddr3 memory groups. Web 57 rows 2 rank x4 planar, low profile sdram outline:

From www.codetd.com

First introduction of DDR3 and mig turn Code World Ddr3 Schematic Web this application note provides general hardware and layout considerations for hardware engineers implementing a ddr3. Web this document provides general hardware and layout considerations and guidelines for hardware engineers implementing a ddr3. With altium , you can use the project’s schematic and place a. Document table of contents x. Web ddr3 board design guidelines. Web the keystone dsp memory. Ddr3 Schematic.

From www.laptopschematic.com

HP DV6/DV7 schematic & boardview, DDR3 DIS UT3/UT5 Laptop Schematic Ddr3 Schematic Web this application note provides general hardware and layout considerations for hardware engineers implementing a ddr3. With altium , you can use the project’s schematic and place a. Document table of contents x. Web the keystone dsp memory interface currently supports various configurations as specified in the jedec ddr3 standard. Web 57 rows 2 rank x4 planar, low profile sdram. Ddr3 Schematic.

From www.scribd.com

Lenovo Y330 072424 072423m ddr3 Schematics PDF PDF Bios Ddr3 Schematic Web 57 rows 2 rank x4 planar, low profile sdram outline: With altium , you can use the project’s schematic and place a. Web this document provides general hardware and layout considerations and guidelines for hardware engineers implementing a ddr3. 10.0 x 11.5 shortened dqs, but unequal length. Web this application note provides general hardware and layout considerations for hardware. Ddr3 Schematic.

From www.i-ciencias.com

[Resuelta] montajedelpwb Problema de conectores PCB Ram Ddr3 Schematic Web although ddr can bring improved performance to an embedded design, care must be observed in the. Web the keystone dsp memory interface currently supports various configurations as specified in the jedec ddr3 standard. Web this document provides general hardware and layout considerations and guidelines for hardware engineers implementing a ddr3. Document table of contents x. Web ddr3 board design. Ddr3 Schematic.

From www.youtube.com

PCB Layout Fast Forward DDR3 Memory Layout YouTube Ddr3 Schematic Web the keystone dsp memory interface currently supports various configurations as specified in the jedec ddr3 standard. Web although ddr can bring improved performance to an embedded design, care must be observed in the. With altium , you can use the project’s schematic and place a. Web altium designer ® provides robust tools for creating ddr3 memory groups. Web this. Ddr3 Schematic.

From www.reddit.com

DDR3 layout vs Memory chip fitting r/robertferanec Ddr3 Schematic Web 57 rows 2 rank x4 planar, low profile sdram outline: 10.0 x 11.5 shortened dqs, but unequal length. With altium , you can use the project’s schematic and place a. Web altium designer ® provides robust tools for creating ddr3 memory groups. Web ddr3 board design guidelines. Web although ddr can bring improved performance to an embedded design, care. Ddr3 Schematic.

From www.laptopschematic.com

HP DV6/DV7 schematic & boardview, DDR3 UMA UT3/UT5 Laptop Schematic Ddr3 Schematic Document table of contents x. With altium , you can use the project’s schematic and place a. Web altium designer ® provides robust tools for creating ddr3 memory groups. Web this application note provides general hardware and layout considerations for hardware engineers implementing a ddr3. Web the keystone dsp memory interface currently supports various configurations as specified in the jedec. Ddr3 Schematic.

From www.laptopserviz.bg

SHUTTLE A14IM01_DDR3 schematic for 5.52 in SHUTTLE LAPTOP SCHEMATICS Ddr3 Schematic Document table of contents x. Web ddr3 board design guidelines. Web the keystone dsp memory interface currently supports various configurations as specified in the jedec ddr3 standard. Web although ddr can bring improved performance to an embedded design, care must be observed in the. With altium , you can use the project’s schematic and place a. Web this application note. Ddr3 Schematic.

From e2e.ti.com

66AK2G02 Question for DDR3 schematic review Processors forum Ddr3 Schematic 10.0 x 11.5 shortened dqs, but unequal length. Document table of contents x. Web 57 rows 2 rank x4 planar, low profile sdram outline: With altium , you can use the project’s schematic and place a. Web ddr3 board design guidelines. Web this document provides general hardware and layout considerations and guidelines for hardware engineers implementing a ddr3. Web the. Ddr3 Schematic.

From realschematic.com

Toshiba Satellite A500 / A505 (DDR3) schematic boardview Ddr3 Schematic With altium , you can use the project’s schematic and place a. Web this document provides general hardware and layout considerations and guidelines for hardware engineers implementing a ddr3. Web ddr3 board design guidelines. Document table of contents x. Web this application note provides general hardware and layout considerations for hardware engineers implementing a ddr3. 10.0 x 11.5 shortened dqs,. Ddr3 Schematic.

From blog.csdn.net

DDR3 SDRAM分析_ddr3地址CSDN博客 Ddr3 Schematic Web this document provides general hardware and layout considerations and guidelines for hardware engineers implementing a ddr3. Web this application note provides general hardware and layout considerations for hardware engineers implementing a ddr3. Web altium designer ® provides robust tools for creating ddr3 memory groups. Web the keystone dsp memory interface currently supports various configurations as specified in the jedec. Ddr3 Schematic.

From e2e.ti.com

AM5728 EVM Schematic DDR3 data line mixed connected Processors Ddr3 Schematic Web although ddr can bring improved performance to an embedded design, care must be observed in the. With altium , you can use the project’s schematic and place a. Web 57 rows 2 rank x4 planar, low profile sdram outline: Document table of contents x. Web the keystone dsp memory interface currently supports various configurations as specified in the jedec. Ddr3 Schematic.

From thetechstall.com

HP Probook 4530s 4730s HM65 DDR3 6050A2465501 Rev X01 Schematic Diagram Ddr3 Schematic Web this document provides general hardware and layout considerations and guidelines for hardware engineers implementing a ddr3. Document table of contents x. With altium , you can use the project’s schematic and place a. Web the keystone dsp memory interface currently supports various configurations as specified in the jedec ddr3 standard. Web although ddr can bring improved performance to an. Ddr3 Schematic.

From www.laptopserviz.bg

QUANTA Y0DE DDR3 SKYLAKE ULT REV1.A SCHEMATIC for 5.52 in QUANTA Ddr3 Schematic Web this application note provides general hardware and layout considerations for hardware engineers implementing a ddr3. Web although ddr can bring improved performance to an embedded design, care must be observed in the. Web 57 rows 2 rank x4 planar, low profile sdram outline: Web the keystone dsp memory interface currently supports various configurations as specified in the jedec ddr3. Ddr3 Schematic.

From thetechstall.com

Zenith UMA DDR3 Schematic Diagram Archives The Tech Stall Ddr3 Schematic Web the keystone dsp memory interface currently supports various configurations as specified in the jedec ddr3 standard. Web although ddr can bring improved performance to an embedded design, care must be observed in the. With altium , you can use the project’s schematic and place a. Document table of contents x. Web ddr3 board design guidelines. Web this application note. Ddr3 Schematic.

From e2e.ti.com

DDR3 Address lines with AM3352 Processors forum Processors TI E2E Ddr3 Schematic Web ddr3 board design guidelines. Web this application note provides general hardware and layout considerations for hardware engineers implementing a ddr3. Web 57 rows 2 rank x4 planar, low profile sdram outline: Web although ddr can bring improved performance to an embedded design, care must be observed in the. Web altium designer ® provides robust tools for creating ddr3 memory. Ddr3 Schematic.

From resources.altium.com

How to Route DDR3 Memory and CPU FanOut PCB Design Blog Altium Ddr3 Schematic Web the keystone dsp memory interface currently supports various configurations as specified in the jedec ddr3 standard. Web although ddr can bring improved performance to an embedded design, care must be observed in the. Web altium designer ® provides robust tools for creating ddr3 memory groups. Web this application note provides general hardware and layout considerations for hardware engineers implementing. Ddr3 Schematic.

From itecnotes.com

Unused Bits on a DDR3 Chip Valuable Tech Notes Ddr3 Schematic Web altium designer ® provides robust tools for creating ddr3 memory groups. Web 57 rows 2 rank x4 planar, low profile sdram outline: Web this application note provides general hardware and layout considerations for hardware engineers implementing a ddr3. Web ddr3 board design guidelines. Document table of contents x. 10.0 x 11.5 shortened dqs, but unequal length. Web this document. Ddr3 Schematic.